摘要

本文通過改變負內(nèi)阻聯(lián)接方法以及接地端的位置,對負內(nèi)阻的串聯(lián)與并聯(lián)形式進行仿真研究,得到了多個基于運算放大器建立的負內(nèi)阻的串聯(lián)與并聯(lián)形式,使負內(nèi)阻的串聯(lián)與并聯(lián)不局限于兩個負內(nèi)阻。該方法可使多個負內(nèi)阻在串聯(lián)與并聯(lián)時表現(xiàn)出與正阻值一樣的特點。該研究結(jié)果明晰了負內(nèi)阻的串聯(lián)與并聯(lián)形式,在電路實驗教學(xué)和工程實踐中具有一定的意義。

關(guān)鍵詞負內(nèi)阻;極性;接地端;串聯(lián)與并聯(lián)形式

Inthispaper,bythemodeofandtheofthe,theandmodesofare,andandmodesofbasedonare,sothattheandmodesofarenottotwo.Inthisway,canshowthesameasinand.Themakecleartheandmodeof,whichhasainand.

“負內(nèi)阻”是一種有源器件,其電阻可視為正數(shù)。該器件可以“中和”正阻值,同時在負阻抗緩沖器、高輸入阻抗放大器、LC振蕩電路以及抵消電路零極點等電路設(shè)計方面起到一定的作用[1,2]。《電路》[3]教材中介紹了基于運算放大器的負內(nèi)阻建立方式,介紹了其特點和使用要點,但是明晰了負內(nèi)阻工作必須在運算放大器的線性區(qū),能夠表現(xiàn)為電阻為“負”的特點。并且,何種情況下負內(nèi)阻的串聯(lián)與并聯(lián)等同于正內(nèi)阻的串聯(lián)與并聯(lián)特點并沒有給出明晰的答案,須要繼續(xù)探究其串聯(lián)與并聯(lián)方式。

文獻[2]對負內(nèi)阻的串聯(lián)與并聯(lián)形式進行了研究,通過仿真剖析,得出了兩個負內(nèi)阻的串聯(lián)和一個負內(nèi)阻與正阻值的串聯(lián)均符合普通正阻值的串聯(lián)關(guān)系:R=R1+R2(R1、R2可為正阻值或負內(nèi)阻)。須要注意的是,當兩個負內(nèi)阻串聯(lián)時,負內(nèi)阻串聯(lián)極性和接地位置具有特殊性。兩個負內(nèi)阻的并聯(lián)和一個負內(nèi)阻與正阻值的并聯(lián)同樣符合普通正阻值的并聯(lián)關(guān)系,滿足1/R=1/R1+1/R2的關(guān)系。文獻[2]的研究對明晰負內(nèi)阻的串聯(lián)與并聯(lián)形式有很大的借鑒意義。

然而在往年的負內(nèi)阻串聯(lián)研究中,缺少針對兩個以上負內(nèi)阻實現(xiàn)串聯(lián)和并聯(lián)的相關(guān)研究,本文通過仿真實驗對多個負內(nèi)阻的串聯(lián)與并聯(lián)進行了研究,總結(jié)了多個負內(nèi)阻的串聯(lián)與并聯(lián)形式。解決這一問題對課堂教學(xué)和工程實踐均有一定的好處。

1負內(nèi)阻的原理

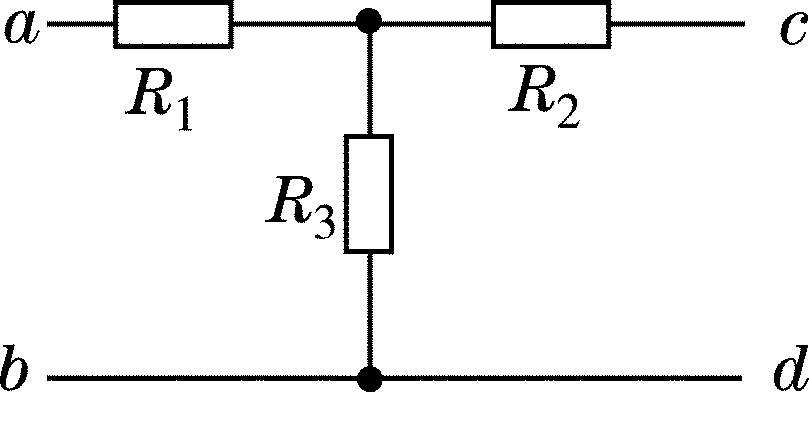

在工程實踐中,單個負內(nèi)阻器件并不常見,一般情況下負內(nèi)阻是基于運算放大器實現(xiàn)的[3],由三個正阻值和運算放大器構(gòu)成,圖1所示為常見的兩種負內(nèi)阻的實現(xiàn)方法[4](Req為從輸入端口看過去的等效內(nèi)阻)。運算放大器工作在線性區(qū)時,整體表現(xiàn)為負內(nèi)阻的特點。

按照運算放大器的“虛短、虛斷”特性[5,6],從輸入端看過去的等效內(nèi)阻為:Req=-R1R3/R2,(R1、R2、R3均為普通的正阻值)。負內(nèi)阻創(chuàng)立的條件為:U0大于等于運算放大器的飽和電流Usat。由電路相關(guān)知識可得:

,且U0

。須要注意的是,負內(nèi)阻和普通正阻值的區(qū)別在于:負內(nèi)阻是基于運算放大器構(gòu)成,且電路中須有接地。

2仿真實驗研究

2.1多個負內(nèi)阻的串聯(lián)研究

在往年的負內(nèi)阻串聯(lián)研究中,主要是針對兩個負內(nèi)阻的串聯(lián)研究,缺乏對兩個以上負內(nèi)阻的串聯(lián)研究。為探究多個負內(nèi)阻的聯(lián)接形式,本文進行了多次仿真實驗。為了防止多個負內(nèi)阻串聯(lián)在一起,導(dǎo)致電路原理圖的復(fù)雜混亂,在仿真過程中使用層次塊替換圖1(a)負內(nèi)阻實現(xiàn)方法1的電路。將圖1(a)中負內(nèi)阻聯(lián)接電路進行封裝,如圖2所示,負內(nèi)阻輸入端口臨近運算放大器反相端的位置標記為“-”,負內(nèi)阻輸入端口臨近運算放大器正相端的輸入端標記為“+”。須要注意的是,在負內(nèi)阻層次塊中不添加接地端。在層次塊添加接地端后,多個負內(nèi)阻串聯(lián)時會導(dǎo)致單個負內(nèi)阻的漏電。為便捷估算,仿真過程中全部使用電阻為-1000Ω的負內(nèi)阻。

與正阻值相比,負內(nèi)阻的特殊點在于極性和接地端。仿真過程中在負內(nèi)阻串聯(lián)電路的不同位置聯(lián)接接地端,接地位置在圖中做相應(yīng)數(shù)字標記。通過電壓表檢測電路電壓,并與參照值進行對比來確定不憐憫況下的接地端位置是否正確。(在端口電流的作用下,當多個負內(nèi)阻串聯(lián)或則并聯(lián)時,總電阻表現(xiàn)為和普通正阻值一樣的串聯(lián)或則并聯(lián)的電阻特點,此情況下的電壓值為“參照值”。)

在兩個負內(nèi)阻的串聯(lián)關(guān)系中,兩個負內(nèi)阻的“-”連接在一起,在兩個以上負內(nèi)阻的聯(lián)接中“+”與“-”能否聯(lián)接在一起需進一步研究,因而對不同極性的聯(lián)接形式進行重新組合剖析。仿真過程中,分為四種不憐憫況,檢測在5V電流下串聯(lián)多個-1000Ω內(nèi)阻時電路流過的電壓值,電壓單位為mA,仿真電路圖與實驗數(shù)據(jù)(表1~表4)如下。

(1)聯(lián)接方法1:串聯(lián)負內(nèi)阻個數(shù)為偶數(shù)且串聯(lián)次序為“+-+-+-……+-”,如圖3所示。

(2)聯(lián)接方法2:串聯(lián)負內(nèi)阻個數(shù)為偶數(shù)且串聯(lián)次序為“+--++-……+-”,如圖4所示。

(3)聯(lián)接方法3:串聯(lián)負內(nèi)阻個數(shù)為奇數(shù)且串聯(lián)次序為“+-+-+-……+-”,如圖5所示。

(4)聯(lián)接形式4:串聯(lián)負內(nèi)阻個數(shù)為奇數(shù)且串聯(lián)次序為“+--++-……-+”,如圖6所示。

通過上述比較剖析,發(fā)覺由圖1(a)電路形式建立的多個負內(nèi)阻在串聯(lián)時必須從“+”接入,后接的負內(nèi)阻“-”與“-”相接,“+”與“+”相接,在負內(nèi)阻串聯(lián)極性聯(lián)接形式為“+--++-……-+”;同理可得:基于相同的實驗原理串聯(lián)和并聯(lián)電阻的計算,可以得出由圖1(b)電路形式建立的多個負內(nèi)阻在串聯(lián)時必須從“-”接入,后接的負內(nèi)阻“+”與“+”相接,“-”與“-”相接,負內(nèi)阻極性聯(lián)接方法須為“-++--+……+-”。

在多個負內(nèi)阻串聯(lián)中,接地端只有一個。當串聯(lián)負內(nèi)阻個數(shù)為奇數(shù)時,接地端可在負內(nèi)阻聯(lián)接點之間或則外接的兩個端口的任意一處;當串聯(lián)負內(nèi)阻個數(shù)為偶數(shù)時,接地端只能在整個負內(nèi)阻串聯(lián)部份的外接端口處,且負內(nèi)阻與負內(nèi)阻聯(lián)接點不可接地。

2.2多個負內(nèi)阻并聯(lián)研究

多個負內(nèi)阻并聯(lián)的仿真電路圖和實驗數(shù)據(jù)如圖7和表5所示。

以圖1(a)電路形式的負內(nèi)阻為例,在多個負內(nèi)阻并聯(lián)中,參照文獻[2]中兩個負內(nèi)阻的并聯(lián)方式,模擬了多個負內(nèi)阻的并聯(lián)。通過對比表1~5的實驗數(shù)據(jù)與參照值可知:多個負內(nèi)阻在并聯(lián)時不分辨質(zhì)數(shù)與質(zhì)數(shù),相同極性的端聯(lián)接在一起,R3處須在“-”端接地,即可表現(xiàn)出多個負內(nèi)阻并聯(lián)與多個正阻值并聯(lián)相同的規(guī)律,即1/R=1/R1+1/R2+……+1/Rn。同理可得:基于相同的實驗原理,可以得出由圖1(b)電路形式建立的多個負內(nèi)阻在并聯(lián)時必須從“-”接入,不分辨質(zhì)數(shù)與質(zhì)數(shù),相同極性的端聯(lián)接在一起即可,接地端在“+”。

3結(jié)語

本文通過電路仿真實驗,研究了多個負內(nèi)阻的串聯(lián)與并聯(lián)形式,總結(jié)了多個負內(nèi)阻在串聯(lián)與并聯(lián)時的聯(lián)接特征:對于多個負內(nèi)阻串聯(lián)時,接地端只有一個。而且,當質(zhì)數(shù)個負內(nèi)阻串聯(lián)時,接地端只能在整個負內(nèi)阻串聯(lián)部份的外接端口處的任意一處,且負內(nèi)阻與負內(nèi)阻的聯(lián)接點不可接地;當質(zhì)數(shù)個負內(nèi)阻串聯(lián)時,接地端必須在負內(nèi)阻聯(lián)接點之間或則外接端口的任意一處。對于多個負內(nèi)阻并聯(lián)時,不分辨質(zhì)數(shù)與質(zhì)數(shù)串聯(lián)和并聯(lián)電阻的計算,相同極性的端聯(lián)接在一起即可,接地端在外接端口的低電勢點。當負內(nèi)阻聯(lián)接時滿足以上特定條件和特定的極性聯(lián)接方法時,就可使多個負內(nèi)阻在串聯(lián)及并聯(lián)時表現(xiàn)出與正阻值一樣的串聯(lián)與并聯(lián)特點。

本文的實驗結(jié)果可在電路理論教學(xué)中作為教學(xué)參考,在電路設(shè)計中也具有一定的參考價值。

參考文獻

[1]田社平,孫盾,張峰.負內(nèi)阻及其應(yīng)用[J].電氣電子教學(xué)學(xué)報,2016,38(1):75-76,80.

TIANSP,SUND,ZHANGF.Onandits[J].of&,2016,38(1):75-76,80.(in)

[2]田社平,陳洪亮,張峰.負內(nèi)阻及其串并聯(lián)電路聯(lián)接[J].電氣電子教學(xué)學(xué)報,2007,29(5):16-18.

TIANSP,CHENHL,ZHANGF.andtheirand[J].of&,2007,29(5):16-18.(in)

[3]邱關(guān)源.電路[M].4版.上海:高等教育出版社,2003.

[4]丁晨華,田社平.用實現(xiàn)負內(nèi)阻的仿真和剖析[J].實驗室研究與探求,2008,27(2):63-66,139.

DINGCH,TIANSP.andofby[J].andin,2008,27(2):63-66,139.(in)

[5]李瀚蓀.簡明電路剖析基礎(chǔ)[M].上海:高等教育出版社,2002.

[6]聞躍,高巖,杜普.基礎(chǔ)電路剖析[M].上海:北大學(xué)院出版社,2002.

基金項目:山東省科技計劃項目();山東地委組織部湖南省重點人才項目;國家級學(xué)院生創(chuàng)新創(chuàng)業(yè)訓(xùn)練計劃項目(2)。

通信作者:李穎弢,男,長沙學(xué)院院長,主要從事半導(dǎo)體元件和集成電路研究,;王方聰,男,長沙學(xué)院講師,主要從事電子線路教學(xué)科研工作,研究方向為模擬電路,。

引文格式:霍顯杰,張祎,李永剛,等.負阻值的串聯(lián)及并聯(lián)形式研究[J].化學(xué)與工程,2022,32(1):47-51.

Citethis:HUOXJ,ZHANGY,LIYG,etal.onandof[J].and,2022,32(1):47-51.(in)

END